Upcoming Events

We’re headed to Brussels for the upcoming FOSDEM 2018 event! Our very own Palmer Dabbelt will be speaking on Saturday, Feb. 3. His panel, titled “Igniting the Open Hardware Ecosystem with RISC-V,” will explore the RISC-V ISA, the Rocket Chip processor generator and the state of RISC-V.

Embedded World is also coming up in Nuremberg, and we’ve teamed up with the RISC-V Foundation to sponsor a “passport” program where attendees can visit multiple RISC-V member companies at the show and have a chance to win a HiFive1 board.

Featured Developer

Our view of the world centers around the developer, the engineer, the user, the dreamer. It’s you who are contributing to RISC-V and open-source, making what we would do at SiFive possible.

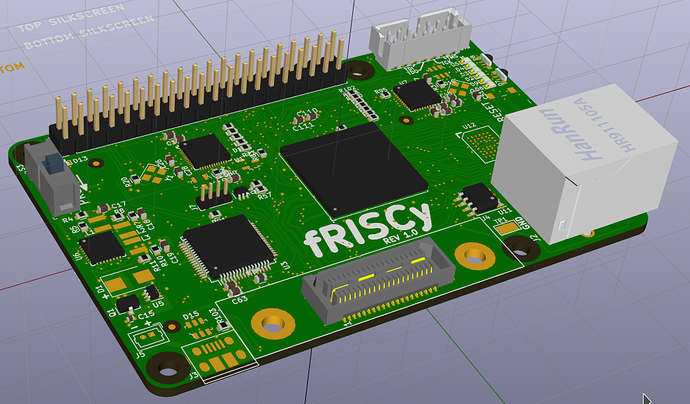

This month’s featured developer is Stephen Newberry. Stephen is a hardware engineer who is passionate about PCB design and VHDL. Pursuing his curiosity around RISC-V and programmable logic, Stephen began working on a board based on the SiFive FE310 and a Xilinx Artix-7 FPGA. Named fRISCy (for FPGA + RISC-V), he hopes the board would be suitable for development and inclusion in industrial embedded systems. We are eagerly following Stephen’s progress on the fRISCy via the SiFive forums and will be excited to see the prototype.

Some of fRISCy’s key features include:

- SiFive FE310 RISC-V Microcontroller (system controller) with 128Mbit QSPI Flash memory

- Xilinx Artix-7 FPGA with SYZYGY Standard carrier-side connector (footprint compatible from XC7A15T to XC7A100T)

- Raspberry Pi form factor and connector placement, including 40-pin GPIO header, RJ-45, and USB Micro-B

- 10/100 Ethernet PHY and 4Mbit SRAM connected via FPGA

- SPI + GPIO interface between FE310 and FPGA for bidirectional data transfer

- FDTI and UART interfaces

We’d love to feature your SiFive project in the next newsletter - let us know what you are working on!

Forum Highlights

The SiFive Forums are buzzing! They are packed with valuable content that can answer your questions and curiosity surrounding RISC-V, development boards, IP evaluations and much more. Here’s a peek at some of the threads that caught our attention (and will now have yours, too!):

More Blog Posts

What’s been on our minds, you ask? Quite a few things, but here are some of our top blogs over the past month:

RISC-V QEMU Part 1: Privileged ISA v1.10, HiFive1 and VirtIO by Michael Clark

A Look Back: 7th RISC-V Workshop by Allen Leibovitch

SiFive Statement on Meltdown and Spectre by Andrew Waterman

SiFive in the Press

Want to see who has been talking about SiFive recently? Let’s take a look!

The Bisquick Alternative by Jim Turley, EE Journal

Getting Started with RISC-V by Daniel Nenni, SemiWiki.com

THE SPARK GAP PODCAST - EPISODE 52 by The Spark Gap Podcast

Year in Review: IP Suppliers Take More RISC-V by Mike Demler, The Linley Group

8 Top Innovations of 2017 by Rick Merritt, EE Times

Engineer Spotlight: Shafy Eltoukhy, Head of SiFive’s DesignShare Program by Chantelle Dubois, AllAboutCircuits.com

SiFive, Microsemi Collaborate on RISC-V Development by Megan Crouse, Product Design & Development

RISC-V in the News

We’re always keeping an eye on RISC-V; after all, our founders invented it! Check out the latest conversations around the RISC-V ISA:

Western Dig, Nvidia On Board with ‘RISC-V,’ So Pay Attention, Says Benchmark by Tiernan Ray, Barron’s

The Jenga Conundrum by Jim Turley, EE Journal

Western Digital to Use RISC-V for Controllers, Processors, Purpose-Built Platforms by Anton Shilov, AnandTech

RISC-V Enables Smart Storage Devices by Tom Coughlin, Forbes

Western Digital Gives A Billion Unit Boost To Open Source RISC-V CPU by Kevin Krewell, Forbes

The Rise of RISC-V on Display at Workshop by William Wong, Electronic Design

Western Digital Transitions to RISC-V Open-Source Architecture for Big Data, IoT

by Chris Wiltz, Design News

Thanks for your continued support!

Until next time,

Jack Kang

We would love to hear from you - reply to this email with any questions or inquiries and we will get right back to you!